Zadowolony

Mikroprocesor składa się z kilku połączonych ze sobą bloków, z których każdy wykonuje określoną funkcję. Projekt i wzajemne powiązania tych bloków nazywane są architekturą. Szybkość, z jaką komputer może odczytywać instrukcje i wykonywać związane z nimi obliczenia, jest określona przez częstotliwość pracy mikroprocesora. Producenci poczynili ogromne postępy w projektowaniu architektury, dzięki czemu komputery są coraz mniej zależne od częstotliwości, co oznacza, że mikro z niższymi częstotliwościami i prędkościami mogą wykonywać więcej obliczeń i zadań. W trakcie ewolucji architektury mikroprocesora przeszedł on ewolucję od architektury jednordzeniowej do wielordzeniowej, zdolnej do przetwarzania kilku informacji jednocześnie.

Historia generacji mikroprocesorów

Fairchild Semiconductor, założony w 1957 roku, wynalazł pierwszy układ scalony w 1959 roku, co dało początek historii mikroprocesorów. W 1968 roku Gordan Moore, Robert Noyce i Andrew Grove opuszczają Dziecięce Targi Półprzewodników i zakładają własną firmę: Integrated Electronics (Intel). W 1971 roku firma wynalazła pierwszy układ Intel 4004.

Obecnie istnieje kilka generacji architektur mikroprocesorów:

- 1. generacja od 1971 do 1973. 1971 INTEL 4004 z prędkością zegara 108 kHz. Inne modele używane w tym okresie to Rockwell International PPS-4, INTEL-8008 i National semiconductors IMP-16, nie były to urządzenia zgodne z TTL.

- II generacja od 1973 do 1978 roku, wdrożono bardzo wydajne 8 bitowe mikroprocesory takie jak Motorola 6800 i 6801, INTEL-8085 i Zilogs-Z80. Ze względu na ich ultraszybkie prędkości były drogie, ponieważ były oparte na technologii NMOS, jednak mimo ceny były bardzo popularne.

- Architektura mikroprocesora trzeciej generacji używana w latach 1979-1980.W tym okresie powstały INTEL 8086/80186/80286 oraz Motorola 68000 i 68010. Procesory te były cztery razy szybsze od swoich poprzedników.

- IV generacja w latach 1981-1995 - powstały 32-bitowe mikroprocesory wykorzystujące HCMOS. INTEL-80386 i Motorola 68020/68030 były popularnymi procesorami.

- 5 generacja rozpoczęła się w 1995 roku i nadal jest na rynku. W tym okresie wprowadzono na rynek 64-bitową nowoczesną architekturę mikroprocesorową, w skład której wchodziły układy Pentium, Celeron, Dual i Quad Core.

Kamienie milowe rozwoju Intel Celeron i Pentium

Intel Celeron został wprowadzony na rynek w kwietniu 1998 roku i należy do serii procesorów Intel X86 dla komputerów osobistych. Jest on oparty na Pentium 2 i może działać na wszystkich programach komputerowych IA-32.

Historia Intel Celeron:

- 4 /01/2000 - Intel Celeron 533.0 MHz;

- 14/02/2000 - Mobile Intel Celeron 450/500 MHz;

- 19/06/2000 - mobilny Intel Celeron niskiego napięcia, 500.0 MHz;

- 3/01/2001 - Intel Celeron, 800 MHz;

- 2001 - Intel Celeron (1,2GHz);

- 2002 - architektura mikroprocesorów Intel Celeron (1.3, 2.10, 2.20 GHz);

- 2003 - procesor mobilny Intel Celeron 2/ 2.55 GHz.

- 2004- Intel Celeron M 320 i 310 (1,3, 1,2 GHz);

- 2008 - Celeron Core 2 DUO (Allendale).

Pentium zostało wprowadzone 2 marca 1993 r. Zastępuje architekturę mikroprocesorów 486 firmy Intel, numer 4 oznacza mikroarchitekturę czwartej generacji w historii mikroprocesorów. Pentium odnosi się do jednordzeniowego Intel x 86, który jest oparty na architekturze piątej generacji. Nazwa tego procesora pochodzi od greckiego słowa penta, które oznacza "pięć".

Oryginalny procesor Pentium został zastąpiony przez Pentium MMX w 1996 roku i posiada 64-bitową szynę danych. Standardowa pętla pojedynczego transferu może czytać lub zapisywać do 64 bitów jednocześnie. Cykle Burst odczytu i zapisu są obsługiwane przez procesory Pentium. Są one wykorzystywane do operacji na pamięci podręcznej i przenoszą 32 bajty (rozmiar linii pamięci podręcznej Pentium) w 4 cyklach zegara. Wszystkie operacje w pamięci podręcznej są dla niej pętlami wsadowymi.

Konstrukcja jednostki centralnej

Architektura mikroprocesora posiada wiele urządzeń peryferyjnych produkowanych na jednym chipie. Posiada ALU (arytmetyczna jednostka logiczna), jednostkę sterującą, rejestry, systemy magistralne i zegar do wykonywania zadań obliczeniowych.

Mikroprocesor to pakiet jednoukładowy, w którym szereg użytecznych funkcji jest zintegrowany i zbudowany na jednym krzemowym układzie półprzewodnikowym. Jego architektura składa się z procesora centralnego, modułów pamięci, magistrali systemowej i jednostki I/O. Magistrala systemowa łączy różne bloki, aby ułatwić wymianę informacji. Ponadto składa się z magistrali danych, adresowych i sterujących zapewniających właściwą komunikację, co jest związane z podstawowym pojęciem architektury mikroprocesora.

Procesor centralny składa się z pojedynczy lub Kilka jednostek arytmetyczno-logicznych (ALU), rejestry i jednostka sterująca. Na podstawie rejestrów można również sklasyfikować numer generacji. ALU oblicza wszystkie operacje arytmetyczne, a także logiczne na danych i decyduje o wielkości mikroprocesora, np. 16- lub 32-bitowy.

Blok pamięci zawiera program, jak również dane i jest podzielony na procesor, pamięć podstawową i pamięć dodatkową. Jednostka wejścia i wyjścia łączy podobne peryferyjne urządzenia komunikacyjne z mikroprocesorem w celu odbierania i wysyłania informacji.

Rodzaje mikro w systemach

Istnieje kilka rodzajów architektur mikroprocesorów dostępnych do zastosowania w różnych systemach:

- Współprocesory. Jest to dodatkowy mikroprocesor, który działa obok głównego mikroprocesora. Jest on zaprojektowany i zoptymalizowany pod kątem konkretnego zadania i zwiększa szybkość przetwarzania poprzez jednoczesną pracę z głównym. Przykładem tego może być koprocesor matematyczny lub akcelerator zmiennoprzecinkowy.

- Procesor skalarny wykonuje obliczenia dla jednej liczby lub zestawu danych w tym samym czasie, jest on zainstalowany w większości nowoczesnych komputerów i jest znany jako jednowątkowy proces instrukcji lub, w skrócie, SISD.

- Architektura macierzowa współczesnego mikroprocesora, zwana również procesorem wektorowym, pozwala pojedynczej instrukcji operować na wielu punktach danych jednocześnie. Jest znany jako procesor SIMD z pojedynczym rozkazem wielu danych, szeroko stosowany w prognozowaniu pogody i modelowaniu przepływu powietrza.

- Procesor równoległy wykorzystuje niezależne mikro pracować nad na tym samym programie. Rozważany proces jest podzielony na zadania, z których każde może być przetwarzane przez. Wszystko koordynowane przez zaawansowany system operacyjny. Programy muszą być specjalnie napisane do przetwarzania równoległego, w przeciwnym razie niektóre z nich nie będą mogły być ukończone, dopóki inne nie zostaną zamknięte, w zależności od wyniku bieżącego procesu.

Mikroprocesory dzielą się na pięć typów: CISC-Complex Instruction Set, Reduced Instruction Set mikroprocesor RISC, ASIC wyspecjalizowany układ scalony, procesory superskalarne i DSP cyfrowe mikroprocesory sygnałowe.

Procesory te są używane do kodowania i dekodowania wideo lub konwersji DAC (digital to analog) i A/D (analog to digital). Potrzebują mikroprocesora, który jest doskonały w obliczeniach matematycznych. Ten układ procesora jest używany w RADARZE, systemach kina domowego, SONARZE, systemach audio, dekoderach i telefonach komórkowych.

Ewolucja Intel x86

Architektura Intel x86 ewoluowała przez lata. Z 29 000 czterordzeniowych tranzystorowych mikroprocesorów 8086 Procesor Intel Core 2 procesor ma 820 milionów tranzystorów, więc organizacja i technologia produkcji zmieniła się diametralnie.

Niektóre z najważniejszych momentów rozwoju architektury x86:

- 8080 był pierwszym na świecie mikroprocesorem ogólnego przeznaczenia. Posiada mikroprocesorową architekturę pamięci z 8-bitowym przechodząc dane do pamięci. Został on wykorzystany w pierwszym komputer osobisty.

- 8086 - maszyna 16-bitowa, znacznie wydajniejsza od swojej poprzedniczki, posiadała tryb rzeczywisty i 1MB pamięci adresowalnej. Miał on szerszą ścieżkę danych: Rejestry 16-bitowe i większe oraz pamięć podręczna lub kolejka poleceń, które zostały wybrane przed wykonaniem.

- 80286 - posiada 16MB adresowalnej pamięci i zawiera dwa tryby: tryb rzeczywisty i tryb 16-bitowy pierwszej generacji. Ma on 16-bitową szerokość danych i model programowy jest również 16-bitowy.

80286: 16 bit microprose

W zasadzie to mikroprocesor, był rozszerzoną wersją 8086. Więc zanim, jak rozumieć 80286, musisz mieć minimalną wiedzę na temat 8086. Intel 8086 był 16-bitowym mikroprocesorem przeznaczonym do stosowania jako CPU w mikrokomputerach. Termin 16 bit oznacza, że jego jednostka arytmetyczno-logiczna, wewnętrzne rejestry i instrukcje są zaprojektowane do obsługi 16 bitowych kodów binarnych. Posiada 20-bitową szynę adresową i 16-bitową szynę danych. Oznacza to, że może uzyskać dostęp do każdej z 1048576 lokalizacji pamięci i może odczytywać lub zapisywać dane do pamięci i portów po 16 lub 8 bitów na raz.

Architektura mikroprocesora 80286 jest specjalnie zaprojektowana dla wielu użytkowników i wielozadaniowości. Posiada cztery poziomy ochrony pamięci i obsługuje system operacyjny. Jego wydajność jest ponad dwa razy większa na cykl zegara niż w przypadku poprzedników Intela 8086/8088. Złożone operacje matematyczne zajmują mniej cykli zegara w porównaniu z 8086. Eliminuje multipleksowanie magistrali i posiada liniową szynę adresową z 24 liniami adresowymi, która może bezpośrednio przenieść 16 MB pamięci. Obsługuje to moduł zarządzania pamięcią, a poprzez niego może oddać 1GB pamięci, zwanej też wirtualną. Procesor zawiera różne wbudowane mechanizmy, które mogą chronić oprogramowanie systemowe przed programami użytkownika i ograniczać dostęp do pewnych obszarów pamięci.

Istnieją dwa tryby pracy układu 80286. Tryb adresu rzeczywistego i tryb chronionego adresu wirtualnego. Zasadniczo w tym trybie jeden użytkownik nie przeszkadza drugiemu. Nie mogą też ingerować w system operacyjny. Funkcje te nazywane są ochroną. Układ 80286 zawiera cztery bloki przetwarzania:

- Jednostka autobusowa.

- Jednostka instrukcyjna.

- Blok czasowy.

- Blok adresowy.

Podczas wykonywania bieżącej instrukcji, BU wstępnie wybiera instrukcję s i zapisuje ją w kolejce sześciu bajtów. Funkcja U polega na dekodowaniu wyróżnionych instrukcji i utrzymywaniu kolejki trzech zdekodowanych instrukcji. Blok adresowy oblicza adres pamięci lub urządzeń I/O, który ma być wysłany dla operacji odczytu i zapisu. Wszystkie cztery jednostki działają równolegle w ramach procesora. Taka implementacja predykcji przejść w architekturze mikroprocesorowej nazywana jest potokiem.

Kolejnym kierunkiem ewolucji był mikroprocesor 80386, pierwsza 32-bitowa maszyna Intela. Ze względu na swoją architekturę był w stanie konkurować ze złożonością i mocą wprowadzonych kilka lat wcześniej mikrokomputerów i mainframe`ów. Był to pierwszy procesor obsługujący wielozadaniowość i zawierający 32-bitowy tryb bezpieczny. Implementuje koncepcję stronicowania. Miał 4 GB adresowalnej pamięci fizycznej i 32-bitową szerokość danych.

80486: technologia buforowania

Później w 1989 Na rynek wszedł mikroprocesor 80486, który wprowadził koncepcję technologii buforowania i potokowego przetwarzania instrukcji. Zawierał on funkcję ochrony przed zapisem i oferował wbudowany koprocesor matematyczny, który wykonywał złożone operacje z główny procesor.

Odmiany Micro Gen 4:

- Pentium - zastosowanie technik superskalarnych zostało wprowadzone, gdy kilka instrukcji zaczęło działać równolegle. Funkcja Page size expansion (PSE) została dodana jako drobne ulepszenie stronicowania.

- Pentium Pro - wykorzystuje zmianę nazw rejestrów, przewidywanie rozgałęzień, analizę przepływu danych, wykonywanie spekulacyjne i inne kroki w potoku. Dodano również zaawansowane techniki optymalizacji mikrokodu oraz pamięć podręczną poziomu 2. Zaimplementowano w nim translację adresów drugiej generacji, w której 32-bitowy adres wirtualny jest tłumaczony na 36-bitowy adres pamięci fizycznej.

- Pentium II. Potrafił on efektywnie przetwarzać dane wideo, audio i graficzne, wykorzystując technologię architektury mikroprocesorów z rodziny Intel MMX (multimedia data set).

- Pentium III - zawiera instrukcje SMD (rozszerzenia strumieniowe) i obsługuje oprogramowanie do grafiki 3D. Ma on maksymalną prędkość zegara procesora 1,4 GHz i zawiera 70 nowych instrukcji.

- Pentium IV - zaimplementowana translacja adresów trzeciej generacji, która przekształca 48-bitowy adres pamięci wirtualnej w 48-bitowy adres pamięci fizycznej. Zawiera inne zmiennoprzecinkowe ulepszenia multimedialne.

- Core - pierwszy mikroprocesor w architekturze rodziny Intel z podwójnym rdzeniem, który jest implementacją dwóch procesorów na jednym układzie i posiada dodatkową technologię obrazowania.

- Core 2 - Rozszerza architekturę do 64-bitów, a Core 2 Quad zapewnia cztery procesory w jednym układzie. Zarówno zestaw rejestrów jak i tryby adresowania są 64-bitowe. Zawiera układ elektroniczny złożony z 1,2 miliona tranzystorów. Jego częstotliwość pracy dla różnych wersji wynosi 25, 33, 66 i 100 MHz. Jest on 3-5 razy szybszy niż 80386. Głównie dostępne w dwóch wersjach: DX i SX. Wersja DX jest 32-bitowym procesorem umieszczonym w 168-pinowej siatce i może pracować z częstotliwościami zegara od 25 do 66 MHz.

Podstawa urządzenia 486

Architektury, na które dzielone są mikroprocesory są złożone i zawierają takie elementy jak schemat blokowy, sposoby dostępu, interfejsy bitowe, format danych i przerwania.

Ważne dodatkowe cechy procesora 486 w porównaniu do 386 są następujące:

- Wbudowany koprocesor matematyczny. W 386 matematyka jest implementowana na zewnętrznym urządzeniu, więc takie instrukcje w 486 są wykonywane trzy razy szybciej.

- 8 kilobajtów kodu i pamięci podręcznej danych na chipie.

- Wysoka precyzja wykonania.

- Jednostka wykonawcza.

- Jednostka sterująca.

- Jednostka interfejsu magistrali.

- Jednostka prefetująca kod.

- Jednostka dekodująca polecenia.

- segmentacja n-jednostkowa.

- Jednostka przywoławcza.

- Blok pamięci podręcznej.

- Jednostka zmiennoprzecinkowa.

- Jednostka prefetowania kodu zawiera 32-bajtową kolejkę składowanie Wyodrębnione kody poleceń.

- Jednostka sterująca zawiera również pamięć ROM do przechowywania mikrokodu. Adres podany w programie nazywany jest adresem logicznym. Zapewnia również 4 poziomy ochrony, aby odizolować i zabezpieczyć zadania i system operacyjny od siebie.

- Skalowalna architektura mikroprocesorowa - koncepcja implikuje okienkowanie.

- Moduł lookup zapewnia wywołanie obiektu wewnątrz segmentu.

- Adres fizyczny. Rzeczywiste pojemności pamięci RAM i ROM, które istnieją w komputerze, są znane jako pamięć fizyczna.

- Jednostka segmentacji i stronicowania reprezentuje jednostkę zarządzania pamięcią.

Bloki RISC

RISC oznacza Reduced Instruction Set Computer i jest rodzajem strategii projektowania architektonicznego procesora. Architektura mikroprocesora RISC odnosi się do sposobu planowania i montażu procesora i może odnosić się do sprzętu lub oprogramowania najbliższego krzemowi, na którym działa. Architektura zestawu instrukcji (ISA) definiuje podstawowe oprogramowanie.

Architektura sprzętu komputerowego wymaga kodu, który rozbija instrukcje na 0 i 1 i który komputer może zrozumieć, znanego również jako kod maszynowy. Architektura procesora może być zupełnie inna, a oprogramowanie ISA będzie to odzwierciedlać. Różnicę między nimi można znaleźć w sposobie obsługi takich zadań jak obsługa rejestrów, przerwań, adresowania pamięci, zewnętrznych wejść i wyjść.

Innymi słowy, kod maszynowy dla jednego nie będzie działał na drugim. Na przykład, pulpit Wersja dla Windows nie będzie działać na smartfonie, ponieważ architektura jest inna. Choć Microsoft zachęca do ewentualnej integracji w jeden system operacyjny dla komputera stacjonarnego Komputery, laptopy i tablety od momentu wprowadzenia systemu Windows 8.

Istnieje kilka typów architektur procesorów i odpowiadających im ISA. Niektóre przykłady RISC to ARM, MIPS, SPARC i PowerPC. Dzisiejsze procesory są wysoce zintegrowane i szybsze, więc zestawy instrukcji RISC stają się coraz bardziej złożone, aby wykorzystać ulepszoną technologię.

Architektura CISC

W celu odpowiadać Na pytanie, co oznacza architektura mikroprocesora CISC, należy rozważyć podejście CISC do liczby wykonywanych instrukcji. Jego głównym celem w tej kwestii jest minimalizacja ilości miejsca na program, przy jednoczesnym poświęceniu liczby cykli. Komputery oparte na architekturze CISC zostały zaprojektowane w celu zmniejszenia kosztów pamięci. Duże programy potrzebują więcej pamięci, co zwiększa koszt. Aby rozwiązać te problemy, można zmniejszyć liczbę instrukcji w programie, mieszcząc wiele operacji w jednej instrukcji, przez co staje się ona bardziej złożona.

MUL ładuje dwie wartości z pamięci do oddzielnych rejestrów w CISC. Mikroprocesor wykorzystuje najmniejszą możliwą liczbę instrukcji podczas implementacji sprzętu i wykonuje operacje.

Główne słowa kluczowe użyte w powyższej architekturze:

- Zestaw instrukcji - grupa instrukcji służących do wykonania programu, który prowadzi komputer poprzez manipulację danymi. Forma: kod operacji (opcode) i operand. Instrukcja jest to instrukcja używana do ładowania i przechowywania danych. operand jest rejestrem pamięci.

- Tryby adresowania są sposobem dostępu do danych. W zależności od rodzaju użytej instrukcji tryby adresowania są różnego rodzaju, np. tryb bezpośredni, w którym uzyskuje się bezpośredni dostęp do danych lub tryb pośredni, w którym uzyskuje się dostęp do lokalizacji danych.

- Wydajność procesora rządzi się podstawowym prawem i zależy od liczby instrukcji, CPI (cykli na instrukcję) oraz czasu cyklu zegara.

Zalety i wady

Według formatu używanych instrukcji możemy wyróżnić główne typy z klasyfikacji architektury mikroprocesorów: RISC i CISC. Zaletą architektury RISC jest to, że posiada ona zestaw instrukcji, więc kompilatory języków wysokiego poziomu mogą tworzyć bardziej wydajny kod. Pozwala to na swobodę miejsca na mikroprocesorach dzięki prostocie. Wiele procesorów RISC używa rejestrów do przekazywania argumentów i przechowywania zmiennych lokalnych. Funkcje używają tylko kilku parametrów, a procesory nie mogą używać instrukcji wywoływania i dlatego używają metody o stałej długości, która jest łatwa do przetłumaczenia.

Szybkość działania może być zmaksymalizowana, a czas wykonania zminimalizowany. Wymaga mniejszej liczby formatów instrukcji, wielu numerów instrukcji, wielu trybów adresowania i dobrej skalowalności. Skalowalna architektura mikroprocesorów wykorzystuje okna rejestrowe do zapewnienia wygodnego mechanizmu przekazywania parametrów między programami i zwracania wyników. Podobny mechanizm jest zaimplementowany w SPARC.

Wady architektury RISC wynikają z faktu, że w głównie wydajność Procesory RISC zależą od programisty lub kompilatora, więc znajomość kompilatora jest niezbędna przy zmianie kodu CISC na kod RISC. Kiedy zmieniasz układ CISC na kod RISC, zwany rozszerzeniem kodu, nastąpi wzrost rozmiaru. A jakość tego rozszerzenia będzie ponownie zależała od kompilatora, jak również zestawu instrukcji maszyny. Wadą jest również pamięć podręczna warstwy 1 procesorów RISC. Procesory te mają większą pamięć cache na samym chipie. Do karmienia instrukcje wymagają bardzo szybkich systemów pamięci.

Zalety architektury CISC - łatwość mikrokodowania nowych instrukcji - pozwoliły konstruktorom uczynić maszyny CISC bardziej kompatybilnymi. W miarę jak każdy z nich stawał się coraz bardziej zaawansowany, do wykonania zadań można było użyć mniej instrukcji.

Wady architektury CISC:

- Wydajność maszyny spadnie, ponieważ czas potrzebny na wykonanie różnych instrukcji będzie różny.

- Tylko 20% istniejących instrukcji jest używanych w typowym zdarzeniu programistycznym, chociaż w rzeczywistości istnieją różne specjalistyczne instrukcje, które często nie są używane.

- Kody stanu są ustawiane przez instrukcje CISC jako efekt uboczny każdej instrukcji, której ustawienie zajmuje czas, a ponieważ kolejna instrukcja zmienia bity kodu stanu, kompilator musi sprawdzić bity kodu stanu, zanim to nastąpi.

Można więc podsumować, że architektura zestawu poleceń jest środowiskiem, które zapewnia połączenie między programistą a sprzętem. Część wykonawcza i kopiowanie danych, usuwanie czy edycja to polecenia własne dla określonego rodzaju architektury mikroprocesora.

Interfejs neurokomputerowy: zasada działania, obszary zastosowań, zalety i wady

Interfejs neurokomputerowy: zasada działania, obszary zastosowań, zalety i wady Laptop z pasywnym chłodzeniem: recenzja, ranking najlepszych, wady i zalety modeli

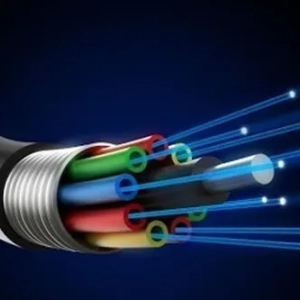

Laptop z pasywnym chłodzeniem: recenzja, ranking najlepszych, wady i zalety modeli Komunikacja światłowodowa: cechy, zalety i wady

Komunikacja światłowodowa: cechy, zalety i wady Podgląd na żywo - co to jest? Zalety i wady w użytkowaniu

Podgląd na żywo - co to jest? Zalety i wady w użytkowaniu Jaka jest różnica między napędem na przednie i tylne koła: różnice, zalety i wady każdego z nich

Jaka jest różnica między napędem na przednie i tylne koła: różnice, zalety i wady każdego z nich Pielęgnacja niemowląt: cele, zalety i wady, porady pediatrów

Pielęgnacja niemowląt: cele, zalety i wady, porady pediatrów Pędzel do akwareli: instrukcja, zalety i wady

Pędzel do akwareli: instrukcja, zalety i wady Gęstość wełny mineralnej: klasyfikacja, zalety i wady, przeznaczenie wełny mineralnej i jej zastosowanie

Gęstość wełny mineralnej: klasyfikacja, zalety i wady, przeznaczenie wełny mineralnej i jej zastosowanie Maalox lub almagel: skład preparatów, przeznaczenie, wady i zalety stosowania

Maalox lub almagel: skład preparatów, przeznaczenie, wady i zalety stosowania